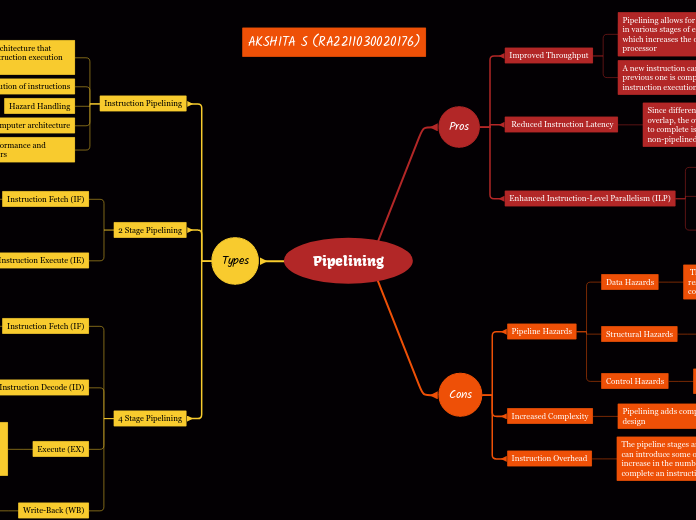

Pipelining

Pros

Improved Throughput

Pipelining allows for multiple instructions to be in various stages of execution simultaneously, which increases the overall throughput of the processor

A new instruction can be started before the previous one is completed, leading to higher instruction execution rates.

Reduced Instruction Latency

Since different stages of instruction execution overlap, the overall time taken for an instruction to complete is significantly shorter compared to a non-pipelined processor.

Enhanced Instruction-Level Parallelism (ILP)

Pipelining is one of the techniques that enhances ILP

Allows a processor to execute multiple instructions simultaneously

This is particularly useful for executing different types of instructions (e.g., arithmetic, memory access) in parallel.

Cons

Pipeline Hazards

Data Hazards

These occur when an instruction depends on the result of a previous instruction that has not yet completed its execution

Structural Hazards

These result from resource conflicts when multiple instructions require the same hardware resource simultaneously. Structural hazards can lead to pipeline stalls or require additional hardware to alleviate the conflicts.

Control Hazards

These occur when there is a branch instruction that changes the order of instruction execution.

Increased Complexity

Pipelining adds complexity to the processor design

Instruction Overhead

The pipeline stages and associated control logic can introduce some overhead, leading to a slight increase in the number of clock cycles required to complete an instruction.

Types

Instruction Pipelining

Key technique in computer architecture that enhances the efficiency of instruction execution in a processor

Allows for overlapping execution of instructions

Hazard Handling

Fundamental concept in computer architecture

Plays a crucial role in the performance and efficiency of modern processors

2 Stage Pipelining

Instruction Fetch (IF)

In this stage, the processor fetches the next instruction from memory. It usually involves reading the instruction from memory or cache and updating the program counter to point to the next instruction.

Instruction Execute (IE)

In this stage, the processor executes the instruction fetched in the previous stage. Execution may involve operations like arithmetic computations, data manipulation, or control flow decisions.

4 Stage Pipelining

Instruction Fetch (IF)

this stage, the processor fetches the next instruction from memory or cache. It involves reading the instruction from memory, updating the program counter, and preparing the instruction for the subsequent stages.

Instruction Decode (ID)

In this stage, the processor decodes the fetched instruction to determine its type and the required operations. This stage also identifies any operands and registers needed for the instruction.

Execute (EX)

In this stage, the processor performs the actual execution of the instruction. This can involve arithmetic and logic operations, data manipulation, or control flow decisions, depending on the instruction

Write-Back (WB)

In this final stage, the processor writes the results of the executed instruction back to registers or memory. This stage ensures that the effects of the instruction are properly stored for subsequent instructions.